Design and Development of ALU using Multi Chiplet Methodology for High-Performance Computing

DOI:

https://doi.org/10.12928/biste.v8i1.14107Keywords:

CMOS, Multi-Chip Module, ALU, Booth MultiplierAbstract

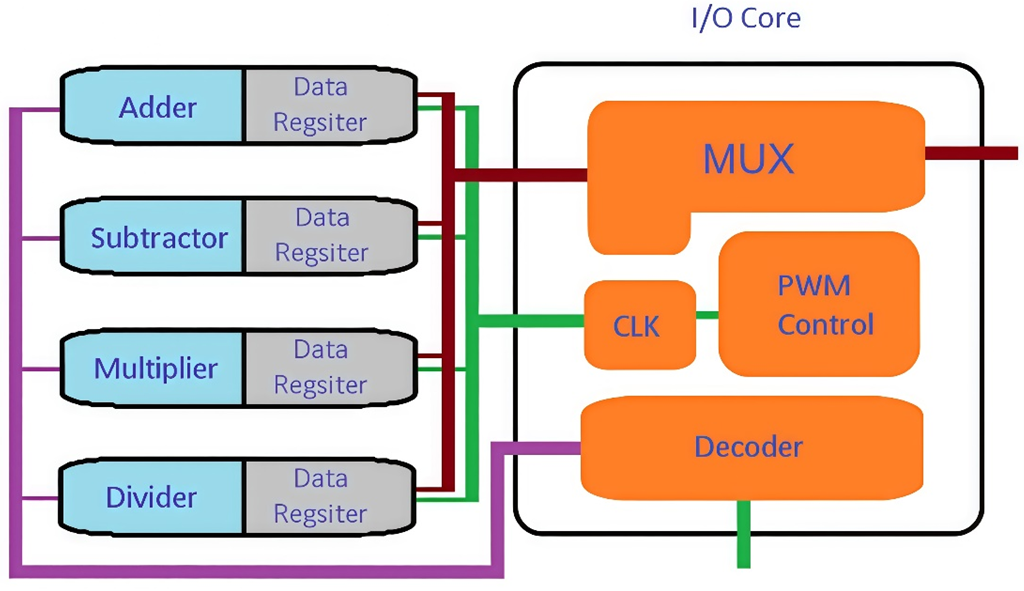

The fundamental programmable logic unit (PLU) in any microprocessors or a microcontrollers and real-time processor of integrated circuits is the arithmetic and logical unit (ALU). The conventional ALUs had exorbitant power consumptions, route delays, and transistor counts because they were created using complementary metal oxide semiconductor (CMOS) technology. Therefore, the motivation of this paper is on the design and development of ALU using Multi Chiplet design Methodology with FPGA kit and simulation is perform on vivado software. Multi-Chiplet systems helps reduce the cost of chip design, low power consumption and increases yield for complicated SoCs (System on Chips). Low power with less design space semiconductors will be the future of computing as the power requirements and size of the SoC cannot be expanded above the set limit. There is a need to reconsider how the design ALU to shorten the time needed for their development as designer continue to push the current limit boundaries of the present CMOS process. This paper proposed a Multi Chiplet SoC structure of ALU with low power, less area required and in small packaging for mostly used in CPU of all type computing devices. The basic function of ALU is to perform arithmetic and Logic operations, required multiplication and additions. In this paper booth multiplier and Kogee-Stone Adder are proposed with multi-chip module (MCM) for low power consumption, less area requirement, high processing speed and less delay. Due to the ever-growing requirements of increasing the Floating-Point Operations per Second (FLOPs) of the processing unit in the field of high-performance computing and AI, there needs to be changes in both the overall design and also the design methodology in fabricating an ALU.

References

S. J. S. Chelladurai, R. Florance, D. Prabhakar, B. Mishra, and M. Kumar, "Design and Implementation of ALU Using Graphene Nanoribbon Field-Effect Transistor and Fin Field-Effect Transistor," Journal of Nanomaterials, 2022, https://doi.org/10.1155/2022/3487853.

I. A. Khan, O. A. Shah, D. Nandan, A. Rai, and A. Mahajan, “Power Efficient Counter Design using CNTFET with AI Integration,” Recent Advances in Electrical & Electronic Engineering (Formerly Recent Patents on Electrical & Electronic Engineering), vol. 18, no. 10, pp. 2069–2082, 2025, https://doi.org/10.2174/0123520965358804241209095031.

Y. Feng and K. Ma, "Chiplet Actuary: A Quantitative Cost Model and Multi-Chiplet Architecture Exploration," In Proceedings of the 59th ACM/IEEE Design Automation Conference, pp. 121-126 2022, https://doi.org/10.1145/3489517.3530428.

O. A. Shah, I. Ahmed Khan, G. Nijhawan and I. Garg, "Low Transistor Count Storage Elements and their Performance Comparison," 2018 International Conference on Advances in Computing, Communication Control and Networking (ICACCCN), pp. 801-805, 2018, https://doi.org/10.1109/ICACCCN.2018.8748364.

A. Singh and S. Singh, "Lanthanum doped BiFeO₃/ZrO₂ gate stack for ferroelectric field effect transistors," Journal of Materials Science: Materials in Electronics, vol. 31, pp. 16189–16198, 2020, https://doi.org/10.1007/s10854-020-04073-4.

S. Ul Haq, E. Abbasian, A. Darabi, I. Ahmed Khan, O. Ahmad Shah and V. B. Sreenivasulu, "Energy-Efficient Buffer-Based Ternary SRAM Cell With Application to Image Processing," in IEEE Access, vol. 13, pp. 172359-172370, 2025, https://doi.org/10.1109/ACCESS.2025.3616000.

R. H. Vanlalchaka, R. Maity, and N. P. Maity, “A low power design using FinFET based adiabatic switching principle: Application to 16-Bit arithmetic logic unit,” Ain Shams Engineering Journal, vol. 14, no. 4, p. 101948, 2023, https://doi.org/10.1016/j.asej.2022.101948.

A. Singh, C. Rai, and S. Singh, "Effect of insulator layer thickness on electrical properties of Al/BiFeO₃/ZrO₂/p-Si for non-volatile memory applications," Ferroelectrics Letters Section, vol. 47, no. 4–6, pp. 71–75, 2020, https://doi.org/10.1080/07315171.2020.1810984.

S. M. Swamynathan and V. Banumathi, "Design and analysis of FPGA based 32 bit ALU using reversible gates," 2017 IEEE International Conference on Electrical, Instrumentation and Communication Engineering (ICEICE), pp. 1-4, 2017, https://doi.org/10.1109/ICEICE.2017.8191959.

H. Sun et al., "Chiplet Multi-Objective Optimization Algorithm Based on Communication Consumption and Temperature," Electronics, vol. 12, no. 7, p. 1604, 2023, https://doi.org/10.3390/electronics12071604.

W. Deal, X. B. Mei, K. M. K. H. Leong, V. Radisic, S. Sarkozy and R. Lai, "THz Monolithic Integrated Circuits Using InP High Electron Mobility Transistors," in IEEE Transactions on Terahertz Science and Technology, vol. 1, no. 1, pp. 25-32, 2011, https://doi.org/10.1109/TTHZ.2011.2159539.

Y. Zheng, K. Zhang, K. Dai, H. Guo, Y. Kong, and T. Chen, “A 340-GHz frequency multiplier chain based on GaN monolithic integrated circuit technology,” Infrared Physics & Technology, p. 106091, 2025, https://doi.org/10.1016/j.infrared.2025.106091.

D. Sharma et al., "Design and Optimization of 4-Bit Array Multiplier with Adiabatic Logic Using 65 nm CMOS Technologies," IETE Journal of Research, 2023, https://doi.org/10.1080/03772063.2023.2204857.

S. Nayak and A. Rai, "Synthesis and Analysis of Optimal Order Butterworth Filter for Denoising ECG Signal on FPGA," in Information Management and Machine Intelligence (Algorithms for Intelligent Systems), pp. 1-12, 2021, https://doi.org/10.1007/978-981-15-4936-6_39.

L. Gopal, N. S. Mohd Mahayadin, A. K. Chowdhury, A. A. Gopalai and A. K. Singh, "Design and synthesis of reversible arithmetic and Logic Unit (ALU)," 2014 International Conference on Computer, Communications, and Control Technology (I4CT), pp. 289-293, 2014, https://doi.org/10.1109/I4CT.2014.6914191.

S. S. Ahmadpour, N. J. Navimipour, N. U. Ain, F. Kerestecioglu, S. Yalcin, D. B. Avval, and M. Hosseinzadeh, “Design and implementation of a nano-scale high-speed multiplier for signal processing applications,” Nano Communication Networks, vol. 41, p. 100523, 2024, https://doi.org/10.1016/j.nancom.2024.100523.

A. Singh and S. Singh, "Effect of annealing temperature on electrical properties of Al/ZrO₂/p-Si MOS capacitor," Ferroelectrics Letters Section, vol. 48, no. 1-3, 2021, https://doi.org/10.1080/07315171.2021.19231198.

P. K. Mishra et al., "Design and Analysis of Graphene Based Tunnel Field Effect Transistor with Various Ambipolar Reducing Techniques," Computers, Materials & Continua, vol. 76, no. 1, pp. 1309-1320, 2023, https://doi.org/10.32604/cmc.2023.033828.

A. S. Vincentelli et al., "Automated Design of Chiplets," in Proceedings of the 2023 International Symposium on Physical Design, pp. 1-8, 2023, https://doi.org/10.1145/3569052.3578917.

S. S. Chiwande and P. K. Dakhole, "Design and Analysis of Low Power Full Adder using Reversible Logic," 2022 6th International Conference on Electronics, Communication and Aerospace Technology, pp. 146-150, 2022, https://doi.org/10.1109/ICECA55336.2022.10009431.

C. Shylaja, A. Rai, and P. K. Mishra, "Modelling and Simulation of 16-bit Vedic Multiplication Using FPGA," Journal of Physics: Conference Series, vol. 2007, no. 1, p. 012003, 2021, https://doi.org/10.1088/1742-6596/2007/1/012003.

V. P. Miskin, S. S. Kerur, O. P. Sulakhe, H. V. Shahapur, A. G. Deshpande and A. B. Shirasangi, "Performance Metrics Comparison of 8-Bit Adder Architectures in 45nm CMOS," 2025 Third International Conference on Networks, Multimedia and Information Technology (NMITCON), BENGALURU, pp. 1-8, 2025, https://doi.org/10.1109/NMITCON65824.2025.11187477.

P. K. Mishra et al., "SPICE Based Design and Implementation of Digital Circuits Using GALEOR Technique," in Advances in Smart Communication and Imaging Systems, pp. 703-712, 2021, https://doi.org/10.1007/978-981-15-9938-5_65.

P. Bir, S. V. Karatangi, and A. Rai, "Design and implementation of an elastic processor with hyperthreading technology and virtualization for elastic server models," The Journal of Supercomputing, vol. 76, no. 9, pp. 7394-7415, 2020, https://doi.org/10.1007/s11227-020-03174-5.

H. Zhang et al., "The Design of Arithmetic Logic Unit Based on ALM," Procedia Engineering, vol. 29, pp. 1969-1973, 2012. https://doi.org/10.1016/j.proeng.2012.01.245.

M. K. Goel, S. Bharti, P. Kumar, S. Dandotiya, A. Pal, and D. Tripathi, “Comparison of power efficient inverter circuit using adiabatic technique,” In Journal of Physics: Conference Series, vol. 2327, no. 1, p. 012007, 2022, https://doi.org/10.1088/1742-6596/2327/1/012007.

K. S. Tiwari, “Design of generic vedic ALU using reversible logic,” Memories-Materials, Devices, Circuits and Systems, vol. 9, p. 100121, 2035, https://doi.org/10.1016/j.memori.2025.100121.

A. Singh, C. Rai, and S. Singh, "Structural and electrical properties of Al/BiFeO₃/ZrO₂/n-Si structure for non-volatile memory application," Applied Physics A, vol. 126, p. 799, 2020, https://doi.org/10.1007/s00339-020-03978-5.

I. A. Khan et al., "A power-efficient error detection and correction circuit design using Hamming Codes for portable electronic devices," Mathematical Modelling of Engineering Problems, vol. 10, no. 3, pp. 951-956, 2023, https://doi.org/10.18280/mmep.100327.

S. S. Navalgund and P. R. Tonse, "Design, Development and Implementation of ALU, RAM and ROM for 8051 Microcontroller on FPGA using VHDL," International Journal of Computer Applications, vol. 80, no. 1, pp. 8-14, 2013, https://doi.org/10.5120/13823-1280.

A. Kumar, S. Shalini, and I. A. Khan, "Optimized SRAM Cell Design for High Speed and Low Power Applications," in World Congress on Information and Communication Technologies (WICT), pp. 1357-1362, 2011, https://doi.org/10.1109/WICT.2011.6141446.

H. Setiawan, A. Ma’arif, H. M. Marhoon, A.-N. . Sharkawy, and A. . Çakan, “Distance Estimation on Ultrasonic Sensor Using Kalman Filter”, Buletin Ilmiah Sarjana Teknik Elektro, vol. 5, no. 2, pp. 210–217, 2023, https://doi.org/10.12928/biste.v5i2.8089.

Published

How to Cite

Issue

Section

License

Copyright (c) 2025 Amrita Rai, Owais Ahmad Shah, Imran Ahmed Khan, Mubeen Ahmad Khan, Latika Jindal, Piyush Chouhan

This work is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.

Authors who publish with this journal agree to the following terms:

- Authors retain copyright and grant the journal right of first publication with the work simultaneously licensed under a Creative Commons Attribution License that allows others to share the work with an acknowledgment of the work's authorship and initial publication in this journal.

- Authors are able to enter into separate, additional contractual arrangements for the non-exclusive distribution of the journal's published version of the work (e.g., post it to an institutional repository or publish it in a book), with an acknowledgment of its initial publication in this journal.

- Authors are permitted and encouraged to post their work online (e.g., in institutional repositories or on their website) prior to and during the submission process, as it can lead to productive exchanges, as well as earlier and greater citation of published work (See The Effect of Open Access).

This journal is licensed under a Creative Commons Attribution-ShareAlike 4.0 International License.